Instruction Set Architecture eXtensions (here abbreviated as ISAX), sometimes also known as Custom Instructions, are one of the key means to specialize a processor for a specific application domain. They enable, e.g., higher performance or better energy efficiency than realizing the applications using just the generic, general-purpose instruction set.

In Scale4Edge, TUDA works on three key technologies aiming to ease the development and deployment of ISAX:

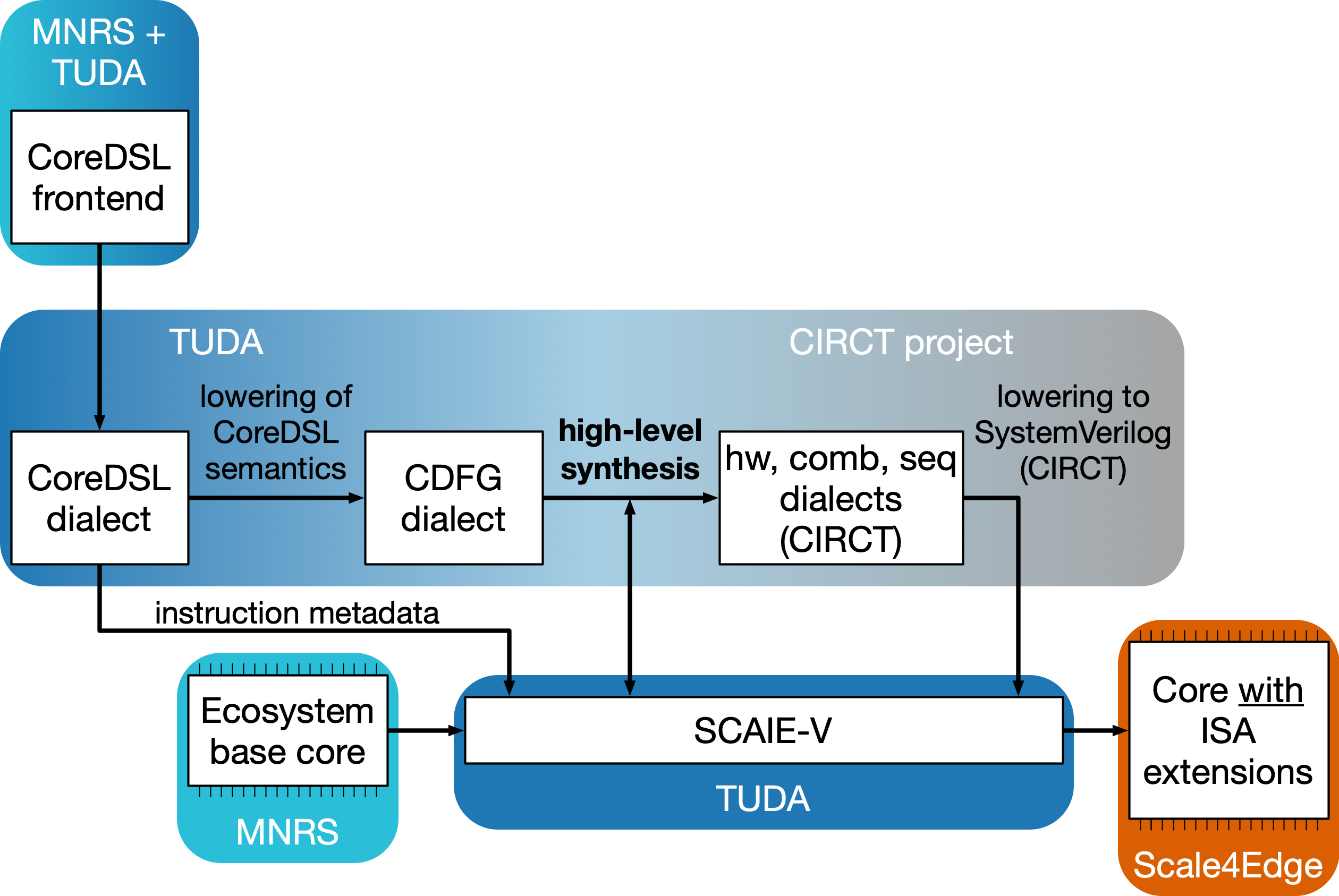

- The first is the Scalable Interface for Instruction Set Extension (SCAIE-V), which provides a standardized interface to add ISA extensions to underlying base processors. The interface is very powerful with regard to the kinds of instructions it allows to be integrated, e.g., even encompassing custom control flow instructions and decoupled execution with dynamic data hazard handling. It is automatically adapted to the needs of the concrete set of ISAX to be added to the base processor, thus avoiding high interface overheads when, e.g., only simple, but already useful, register-type instructions are to be added. The customization of the interface and the integration into the base core is performed by an automatic tool that aims to insert the necessary logic in a "correct-by-construction" manner, leaving the functionality of the base core untouched.

- In close collaboration with Scale4Edge project partner MINRES Technologies, TUDA designed the CoreDSL2 language for describing instruction sets, both generic as well as ISAX, at a high abstraction level. By being based on a C-like syntax, CoreDSL aims to be familiar to users of the resulting processors, such as software developers and tool designers, and does not require any experience in hardware design for productive use. CoreDSL descriptions can serve as the "single source of truth" for a variety of EDA tools. In context of Scale4Edge, it has already been picked up by multiple project partners to create verification and software programming tools.

- TUDA itself is using CoreDSL to create a custom high-level synthesis tool flow, currently code-named Longnail, that aims to automatically generate the actual hardware underlying ISAX described in the language, and integrate it into a base processor core using SCAIE-V. In this manner, domain software experts can easily formulate exactly the functionality required for their applications, and quickly gauge the power-performance-area characteristics of the resulting processor, or create a virtual or FPGA-based prototypes of the customized core for early software development. Longnail relies on state-of-the-art software technology (e.g., LLVM, MLIR, CIRCT) to generate and optimize high-quality hardware from the CoreDSL descriptions.

SCAIE-V has been the subject of a high-ranking conference publication (DAC 2022) and is offered as open-source in https://github.com/esa-tu-darmstadt/SCAIE-V. It has also been used in Scale4Edge to customize a commercial CPU core (TGC_C, provided by Scale4Edge project partner MINRES Technologies) for high-efficiency execution of a neural-network based audio event detection model designed by the project partner Bosch. The resulting chip reaches a clock frequency of over 1 GHz after fabrication in a 22nm ASIC process. TUDA and MINRES will collaborate to enable the use of SCAIE-V in later generations of the commercial MINRES TGC family of processor cores.

CoreDSL is an open specification, available at https://minres.github.io/CoreDSL/, which also provides reference software implementations, e.g., a front-end for reading in and manipulating CoreDSL descriptions. MINRES Technologies has picked up CoreDSL to offer commercial development and support services for CoreDSL-based tools.

With the end of the first phase of the Scale4Edge project, a prototype of the ISAX high-level synthesis tool Longnail has been completed. It already is able to automatically create the ISAX that were used to realize the Bosch neural-network based audio event detection model. Longnail achieves the same implementation quality as the initially manually designed ISAX, but is now using the concise abstract CoreDSL descriptions as tool inputs. In Scale4Edge Phase 2, Longnail will be further refined to become suitable as the base for a productized tool version to be developed and supported by MINRES Technologies.

SCAIE-V and CoreDSL have been open-sourced under a permissive license. Longnail remains proprietary to enable commercial exploitation after the end of Scale4Edge Phase 2.

Embedded Systems and Applications Group (ESA), Technical University of Darmstadt

Prof. Dr.-Ing. Andreas Koch

Hochschulstr. 10

64289 Darmstadt

Deutschland

The CoreDSL language co-developed by TUDA with MINRES Technologies is also used in the ISAX Tools by TUDA, the TGC Core and VPs of MINRES Technologies, as well as in the ETISS verification tools by TUM and the Extensible Compiler by DLR.