Ecosystem Microcontroller

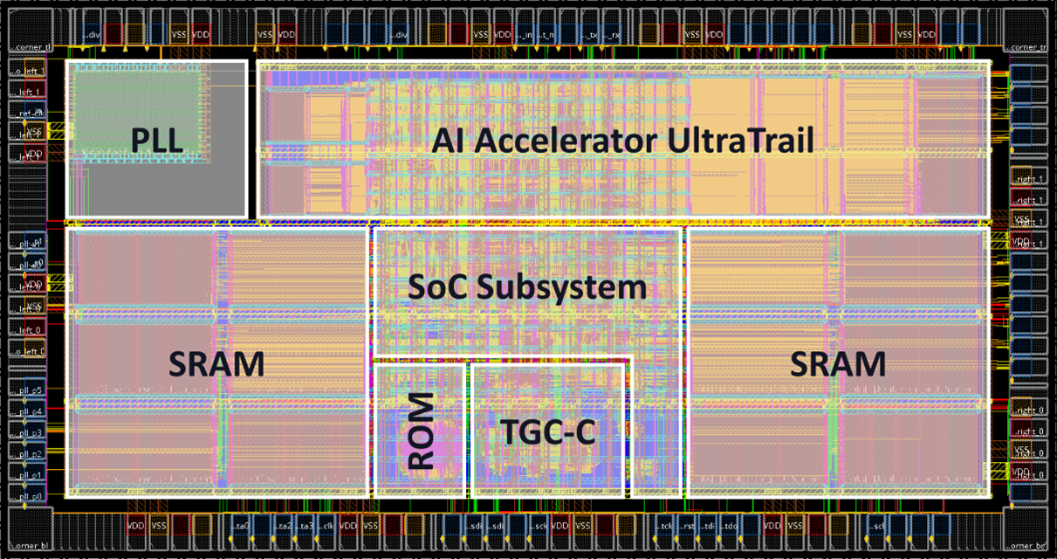

The Ecosystem microcontroller is a PULPissimo-based microcontroller featuring the following Scale4Edge ecosystem IPs:

- A RISC-V TGC processor core

- The AI hardware accelerator UltraTrail

- A phase-locked loop (PLL)

Due to the high configurability of the individual components, the platform can be quickly and easily adapted to specific applications. A specialized ecosystem microcontroller was taped-out in 22nm FDSOI technology as a demonstrator for an audio event detection use-case provided by the project partner Bosch.

FreiTest

FreiTest (developed from PHAETON) is an ATPG (Automatic Test Pattern Generation) Framework based on SAT-Solving (Boolean Satisfiability Problem) and BMC (Bounded Model Checking). It generates Test Patterns and Software-Based Self-Tests (SBSTs) for synthesized circuits and is under active development. First results on achieved Fault Coverages have been published on the IEEE ETS2023 conference in Venice under the title "Constraint-Based Automatic SBST Generation for RISC-V Processor Families".

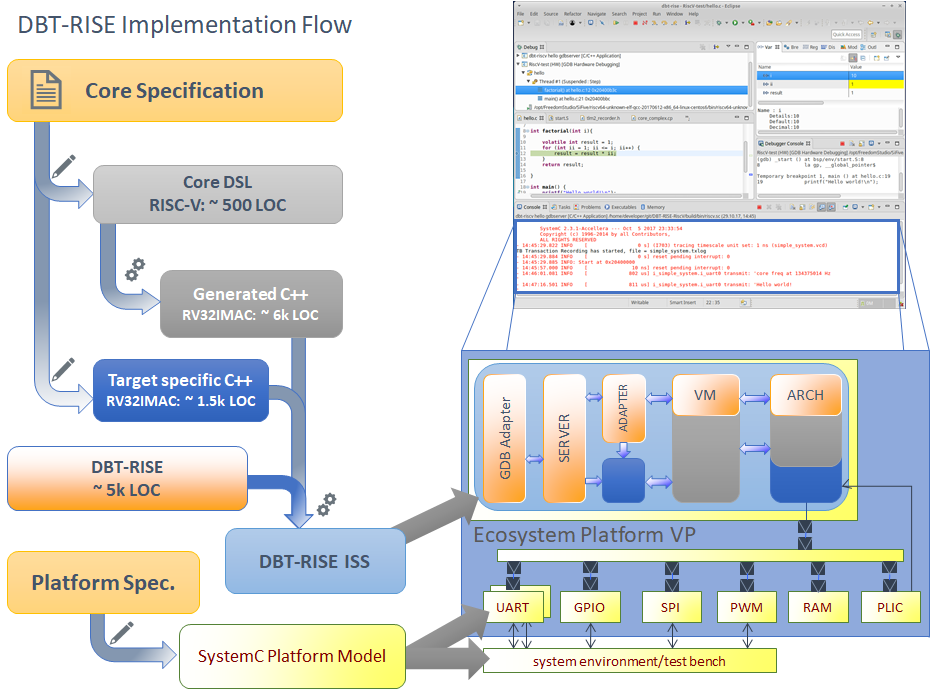

TGC-VP

Based on years of experience developing and integrating SystemC based virtual platforms in the industry, MINRES has created DBT-RISE (Dynamic Binary Translation Re-targetable Instruction Set Simulator), a versatile environment to rapidly implement ISS of any architecture. DBT-RISE serves as basis for the implementation of the TGC (The Good Core) ISS (TGC-VP).

TGC-VP provides the following features:

Apache License 2.0

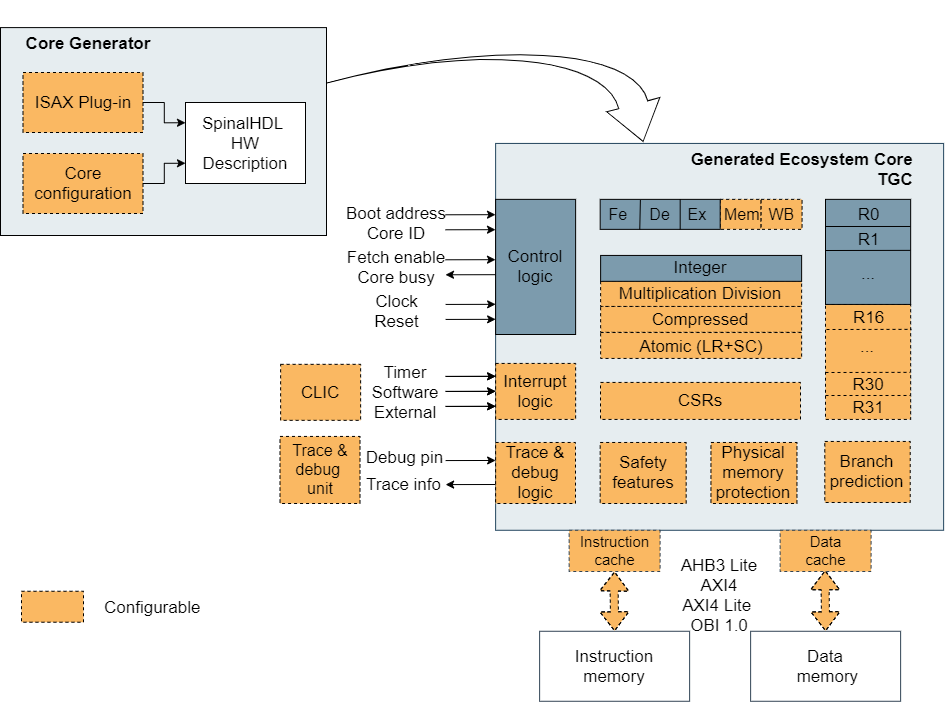

TGC Cores

The Good Folk Series is a highly flexible, scalable and configurable RISC-V based core family developed by MINRES. The standard cores can easily be tailored to specific application requirements using CoreDSL.

It is technology independent, ensures integrity and targets low power edge computing applications. The comprehensive SDK and concise documentation makes it accessible to small and medium companies.

Send an email eyck@minres.com