Not Applicable

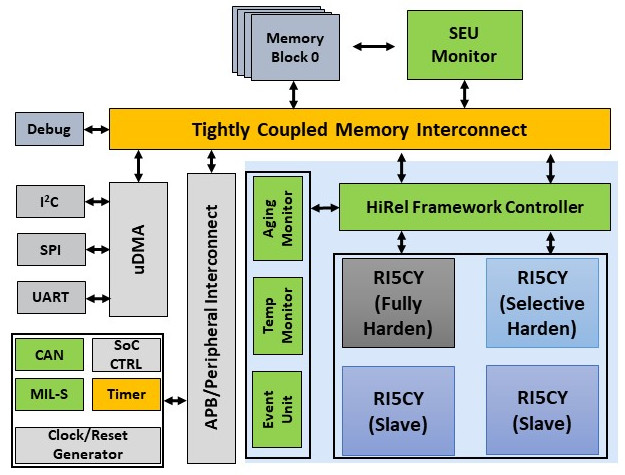

HighRel Multiprozessor

The HighRel Multiprocessor is a Pulpissimo-based quad-core processing system that is specifically built to withstand the harsh environments as they occur in avionics or astronautics. Based on the required processing power as well as different health and environmental monitors, the system is able to autonomously configure itself to various states of fault tolerance (DMR, TMR or QMR) or performance (low power or high performance).

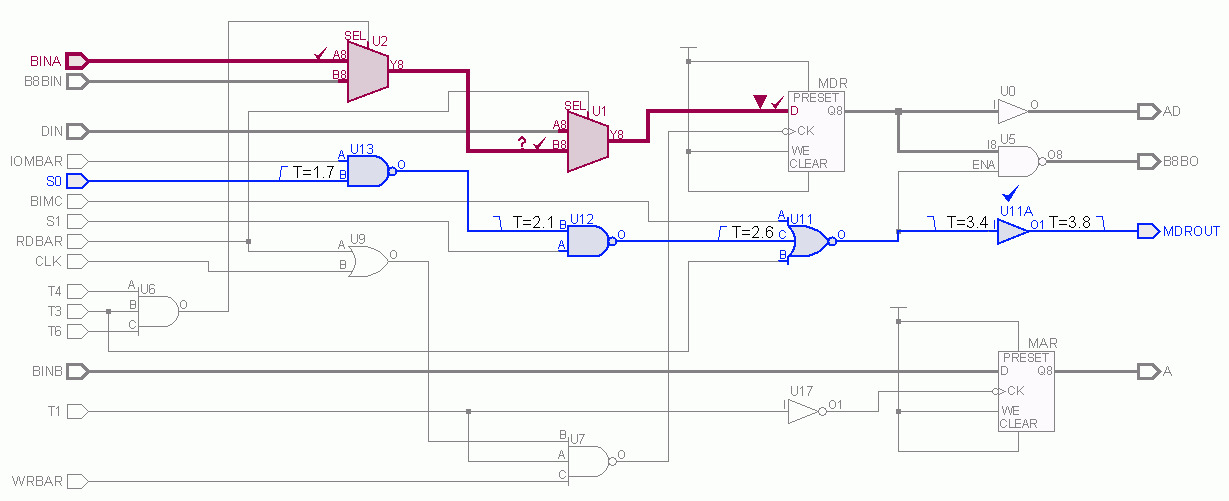

Drawing Engine Nlview

Concept Engineering's Nlview® engine provides automatic generation of schematic diagrams for different levels of electronic circuits, including gate-level, RTL and block-level. Optional engines are available for the system-level (S-engine), for the transistor-level (T-engine), and for automotive and aerospace applications (E-engine).

Commercial licenses can be obtained from Concept Engineering.

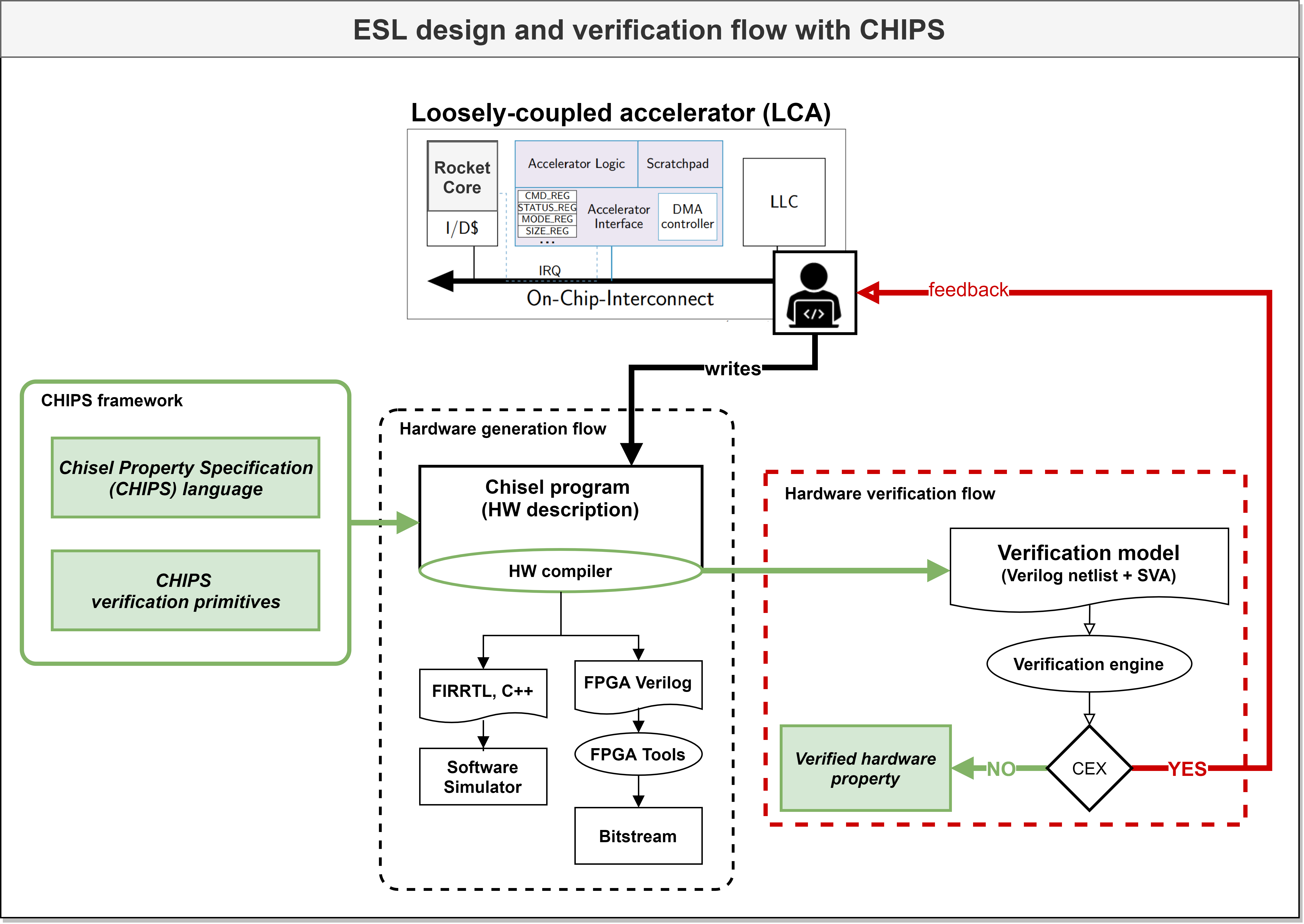

CHIPS Verification Framework

The CHIPS Verification Framework is a collection of tools and libraries for (formal) hardware design verification. The framework encompasses two subprojects:

CHIPS: Chisel Hardware Property Specification Language

The foundation of the CHIPS-VF is a domain-specific language (DSL) embedded in Scala that allows the specification of lightweight verification properties on different levels of abstraction using the assertion-based verification paradigm.

On Chip Debug Solution

Lauterbach implements debugging and trace support in alignment with Partner Infineon specific Hardware Solution.

The Solution will be part of Lauterbach's commercial RISC-V Debug Tools

tflite_micro_compiler

Generate tflite micro code which bypasses the interpreter (directly calls into kernels)

Basically this code uses a fully set up tflite micro instance to dump the internal allocations and function calls assigned to the model, then dumps the tensor and node settings into a compilable file, eliminating the need for running the interpreter at each program start and for resolving the correct kernel at run time.

Apache License 2.0

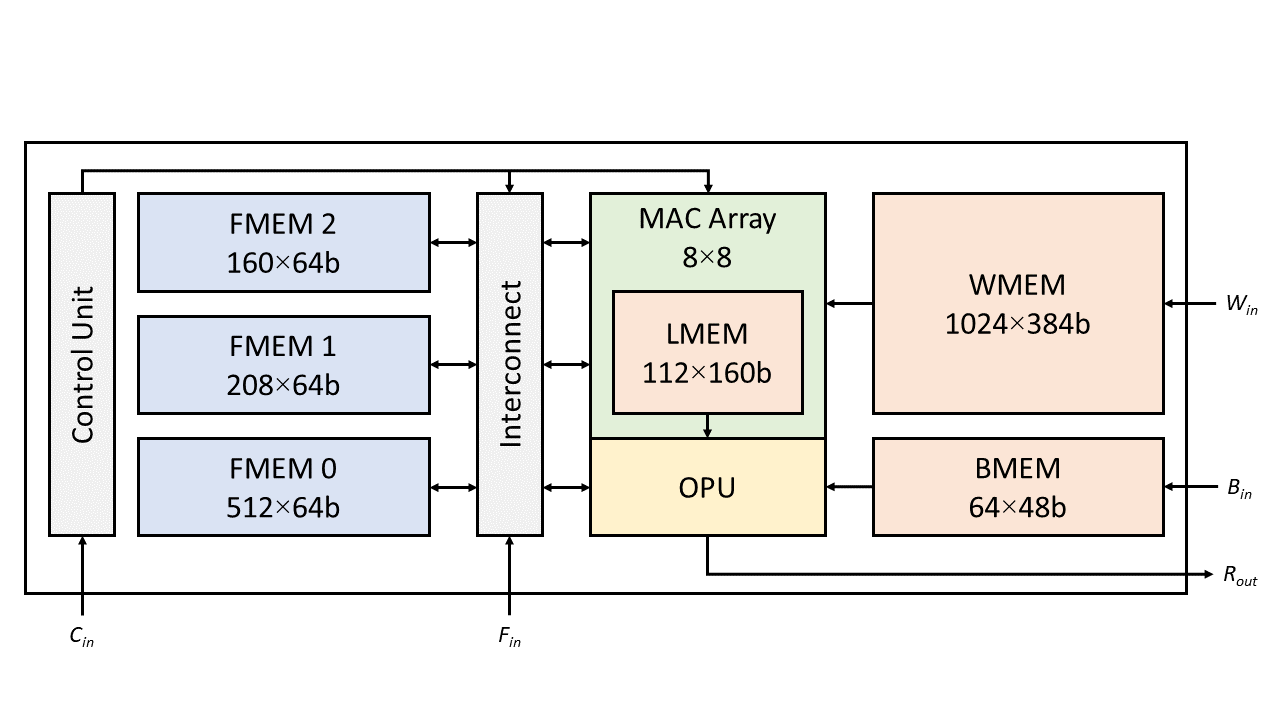

UltraTrail - Ultralow-Power AI Accelerator for Edge Devices

UltraTrail is a configurable hardware accelerator for real-time inference of temporal convolutional networks (TCNs) on edge devices. Designed for near-sensor signal processing on energy-constrained platforms it features an optimized dataflow for one-dimensional convolution with a total power consumption in the low microwatt range. The parameterizable architecture combined with a hardware-aware neural architecture search (NAS) allows an automatic generation of domain-specific accelerator instances. Accurate models for power, performance, and area enable a fast design-space exploration.

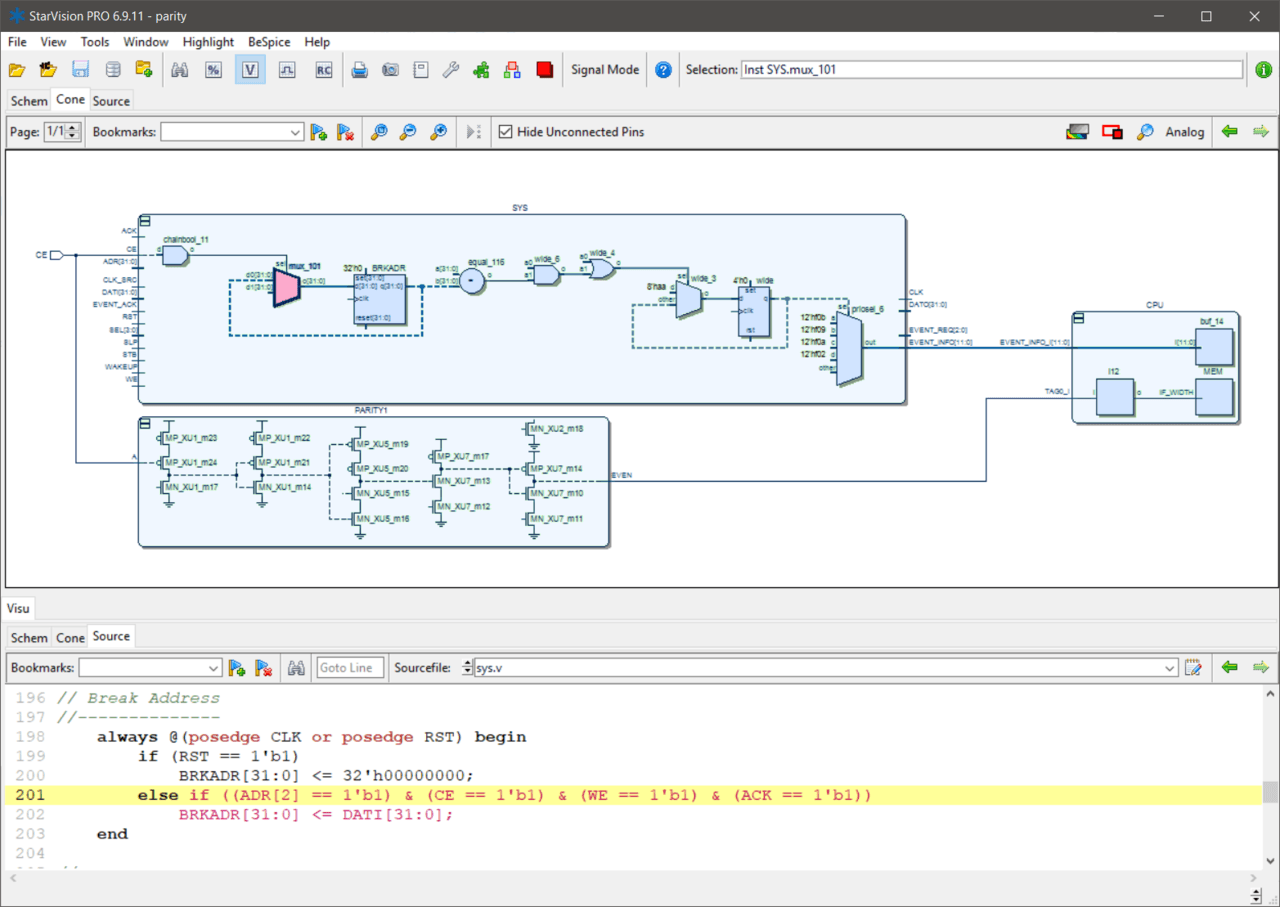

StarVision PRO - Debugging Cockpit for Transistor, RTL, and System-Level Designs

StarVision® PRO represents the state-of-the-art in debug solutions for advanced electronic SoCs. The incorporation of Concept's leading visualization and detection technology enables rapid cause-effect analysis for efficient functional analysis. This advanced and unique mixed-mode debug platform seamlessly combines SPICE and transistor analysis from our market leading SpiceVision PRO tool with digital RTL and gates from our advanced RTLvision PRO tool.

For access to the tool, send an e-mail to info@concept.de with remark "Scale4Edge".